近日,我校先进制造工程学院徐太龙副教授与澳门大学模拟与混合信号超大规模集成电路国家重点实验室合作研发的锁相环芯片发表在集成电路领域国际权威期刊《IEEE Transactions on Circuits and Systems I: Regular Papers》上。

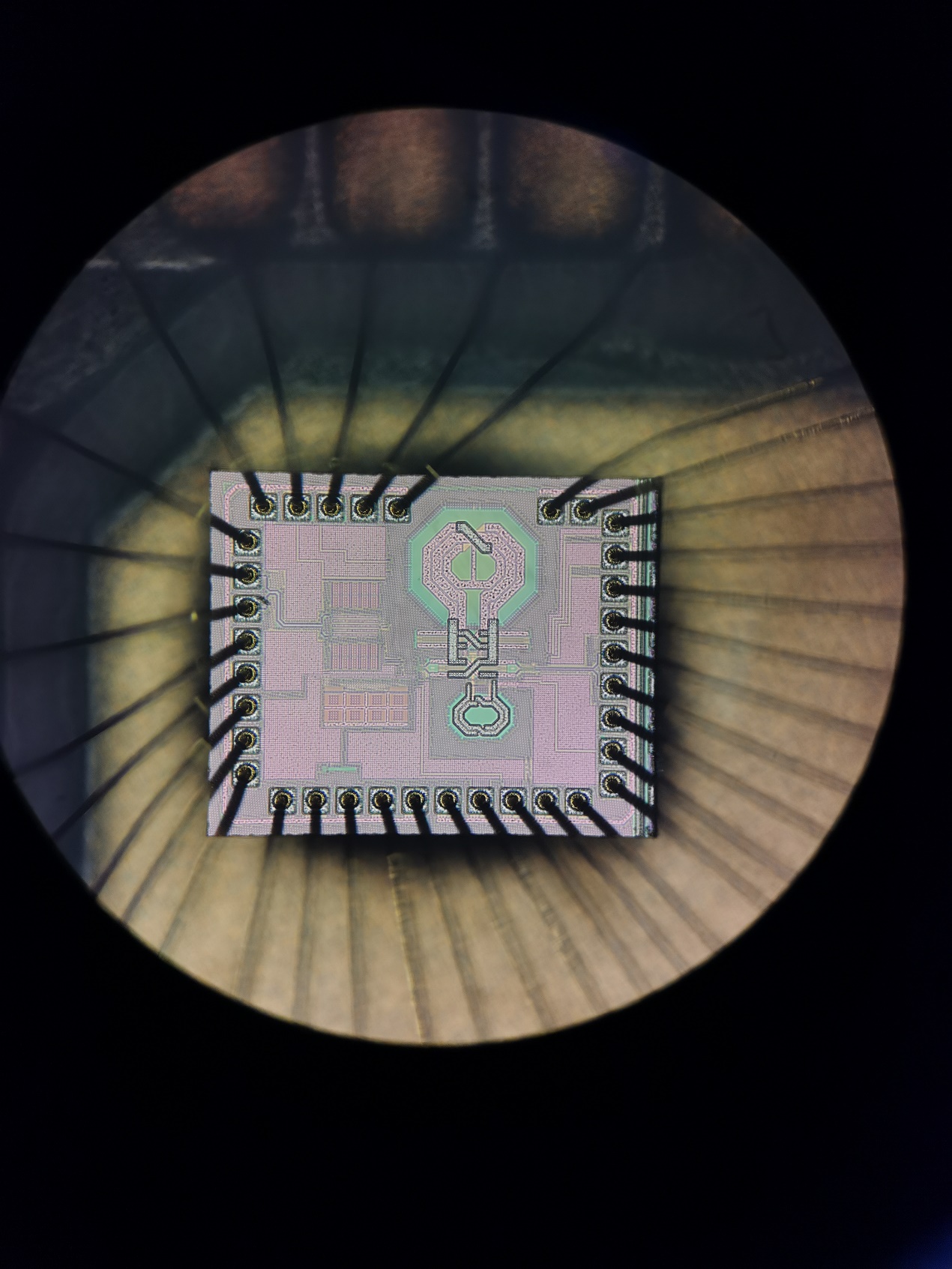

该论文在分析和归纳已有模拟整数锁相环成果的基础之上,提出一种新型增益倍乘鉴相器,改善了参考信号采样锁相环芯片的性能。芯片采用台积电65nm工艺制造,测试性能指标达到预期设计目标。

近年来,随着我校大力建设和发展集成电路科学与工程学科,徐太龙副教授致力于模拟与混合信号超大规模集成电路设计的研究,研究方向为“应用于无线通信收发机的射频/毫米波/太赫兹频率合成器芯片的设计”。我校与澳门大学模拟与混合信号超大规模集成电路国家重点实验室保持紧密的合作关系,并与南方科技大学、电子科技大学和南京邮电大学相关的集成电路设计团队保持着良好的合作关系。

论文链接:https://ieeexplore.ieee.org/document/9872149

澳门大学集成电路国家重点实验室链接:https://ime.um.赌博平台.mo

殷俊副教授个人主页链接:https://ime.um.赌博平台.mo/people/junyin

麦沛然教授个人主页链接:https://ime.um.赌博平台.mo/people/pimak

芯片显微照片

论文主要作者(左:殷俊副教授,中:徐太龙副教授,右:麦沛然教授)

论文首页

撰稿人:胡学友

审稿人:杜 娟